## КАЧЕСТВО

## Тестопригодное проектирование в Остеке?

Естественно!

Текст: Тимофей Максимов

«Сапожник без сапог»! Пожалуй, ни один производитель не захотел бы услышать о себе эту расхожую фразу. Тем более это касается Остека как основного поставщика решений для производства электроники на российском рынке. Их внедрение при разработке и производстве собственных продуктов не вопрос престижа или принципа – это жизненная необходимость.

Остек-Электро - команда профессионалов в технологиях тестирования электроники. В статье на примере собственных разработок компании мы рассмотрим, как с помощью синтеза внутрисхемного тестирования и периферийного (граничного) сканирования электронных модулей добиться 100 % тестопригодности еще на стадии проектирования.

Очевидным и традиционным решением всегда был функциональный контроль. А поскольку вы хорошо знаете своё изделие и знаете, как его проверять, то с легкостью можете спроектировать тестовый стенд. Или нет? В идеальном мире возможно все, но в реальности эффективность и достаточность функционального контроля очень сильно ограничена заложенной в стенд глубиной диагностики, а также универсальностью по отношению к другим выпускаемым изделиям – иначе экономически целесообразным он будет лишь при большой серийности. Российская реальность такова, что крупную серийность на отечественных производствах электроники редко встретишь. С другой стороны, у всех широкая номенклатура изделий. В этих же обстоятельствах живет и Остек-Электро, но имеет преимущество в том, что является поставщиком современных технологических решений в области тестирования и потому пользуется этим преимуществом сполна в собственном проектировании и производстве.

На текущий момент общепринятыми технологиями электрического контроля выпускаемых электронных модулей помимо функционального контроля (FT – functional test) являются внутрисхемное тестирование (ICT – incircuit test) и периферийное сканирование (BS – boundary scan) по стандарту IEEE1149 через интерфейс JTAG. Каждая из них имеет свои достоинства и недостатки, но их совокупность дает выдающийся уровень тестопригодности. Давайте рассмотрим эти технологии.

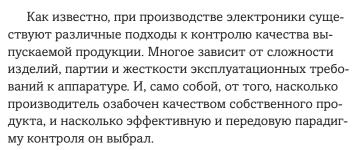

Пример изделия ООО «Остек-Электро» с тестовыми точками

Метод внутрисхемного тестирования (ICT) позволяет проверять компоненты непосредственно в схеме без подачи штатного питающего напряжения. Таким образом выявляются дефекты номиналов электрических компонентов, а также параметрическое функционирование таких компонентов, как диоды, транзисторы, оптопары, реле, трансформаторы и т. д. Сегодня потребность подобного контроля обостряется из-за заполненности рынка ЭКБ контрафактом. Также на ранней производственной стадии выявляются такие грубые дефекты, как КЗ между цепями питания с общей шиной, способные привести к разрушительным последствиям. Для проведения тестирования по методике ІСТ используют тестеры с пробниками – летающими или в адаптере. И если адаптерные тестеры типа «ложе гвоздей» дают высокое быстродействие, то системы с летающими пробниками позволяют гибко подстраиваться под текущие потребности в тестировании изделий.

Популярные на российском рынке установки с летающими пробниками SPEA4060 (рис 1) позволяют обеспечить контакт даже к самым небольшим типоразмерам компонентов, таким как 01005, с обеих сторон платы. Но тем не менее, каждое изделие имеет свои особенности доступа для пробников, что на практике усложняет или ограничивает возможности внутрисхемного тестирования.

В некоторых случаях нежелательно разрушительное физическое воздействие на контактную площадку или вывод компонента даже при использовании функции мягкого касания. Такие несложные на стадии проектирования меры, как выведение тестовых площадок на цепи с внутрисхемным тестированием решают многие проблемы и существенно облегчают подготовку тестовых программ, повышают тестопригодность и увеличивают скорость проверки за счет доступа для всех пробников. На рис 2 приведен пример подоб-

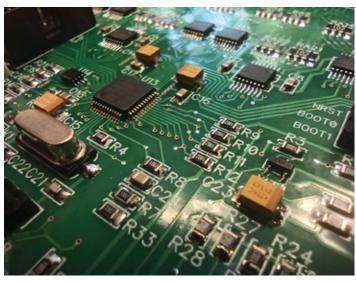

Тестовая развязка Х1 схемы питания

ной модификации на одном из собственных изделий ООО «Остек-Электро». Естественно, на каждом типе изделий предусмотрены реперные знаки с обеих сторон и поля платы с достаточным выносом без цепей и компонентов для беспрепятственной фиксации в рабочей зоне SPEA4060.

Для увеличения тестового покрытия схем преобразования питания предусмотрены развязывающие площадки, позволяющие контролировать работу каждого каскада изолированно. На Рис 3 для проведения контроля несложной схемы DC-DC-преобразователя напряжения VR1 с обвязкой предусмотрен разрыв цепи X1. Таким образом выходное напряжение, ёмкость выходных конденсаторов и напряжение стабилизации TVS-диода можно проверить без какого-либо воздействия относительно потребляющей схемы. Как только внутрисхемный контроль проведен, площадки разрыва X1 спаиваются для дальнейшей работы уже с запитанным изделием. Согласитесь, в большинстве случаев подобная доработка совершенно незначительно усложняет производственный процесс, но при этом сколько преимуществ дает для тестирования!

Однако из-за упора на внутрисхемное тестирование возможности системы ограничены для контроля цифровых схем. Существующие опциональные расширения позволяют подключать изделие через собственные разъемы к цифро-аналоговым модулям, но, во-первых, требуется их наличие в составе системы, а во-вторых, необходима изначальная серьезная проработка как самого изделия, так и тестовой программы.

И здесь на выручку как нельзя кстати приходит технология периферийного (граничного) сканирования, основанная на стандарте IEEE1149. Речь, конечно же, о JTAG-тестировании, не нуждающемся в особом представлении для производителей цифровой электроники. Тем не менее, приведем краткую предысторию возникновения технологии периферийного сканирования и напомним основные принципы работы.

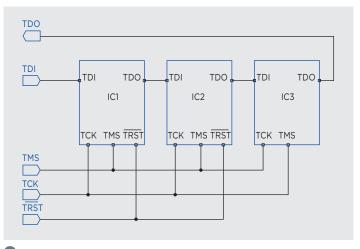

Интерфейс JTAG. Линия TRST в примере предусмотрена только для IC1 и IC2. Обвязка линий JTAG не отображена

В конце прошлого века технология ІСТ стала отставать во всеобщей погоне за миниатюризацией и цифровизацией печатных плат и уже не удовлетворяла всем предъявляемым требованиям к тестированию. В результате поиска новых идей родился метод Boundry Scan и стандарт IEEE1149, буквально открывший новую эпоху в тестировании сложных цифровых устройств. За разработку и развитие стандарта отвечает так называемая группа JTAG (Joint Test Access Group), аббревиатура которой стала прочно ассоциироваться с аппаратным интерфейсом технологии периферийного сканирования. Его структура состоит из четырех обязательных линий с пятой опциональной (рис 4). По линии TMS от JTAG-контроллера отправляются команды, а линия ТСК осуществляет тактирование. Тестовая последовательность, определяющая логическое состояние выводов компонента, задвигается по линии TDI и переходит к следующему компоненту JTAG-цепочки по линии TDO. Сброс JTAG-логики производится по линии или при её отсутствии логической последовательностью по линии TMS. Каждый производитель микроэлектроники сам определяет аппаратную реализацию данного стандарта и описывает её для конкретного компонента, будь то процессор или ПЛИС, с помощью специального языка – BSDL (Boundary Scan Description Language).

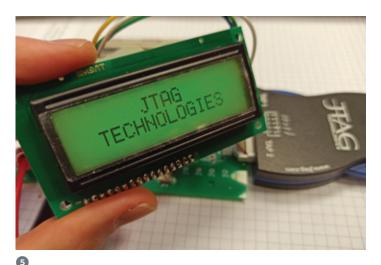

Статус ведущего мирового носителя технологии крепко держит компания JTAG Technologies, Нидерланды. Богатый функционал и широкий спектр их решений, а также сильная поддержка клиентов есть и на российском рынке.

Мы стали использовать возможности технологии периферийного сканирования на основе станций JTAG Technologies, как только начали сами разрабатывать цифровые устройства с использованием компонентов с поддержкой стандарта IEEE1149. Насколько изделие тестопригодно можно оценить уже на стадии создания электронной принципиальной схемы. Достаточно экспортировать её в формате нетлиста (Tango, Protel

Оснастка входного контроля микроконтроллеров STM32

2.0, PDIF, ODB++ и т.д.) и загрузить в программу JTAG ProVision™, где легко проводится анализ схемы и компонентов на наличие тестовых моделей и доступа к цепям. Взглянув на изделие с нового угла, разработчик может не только немного доработать схему и повысить тестовые возможности, но и найти схемотехнические ошибки, ведь программа дает обратную связь по конфликтам в цепях. Именно поэтому при создании нового изделия тестопригодность мы оцениваем уже на ранней стадии до заказа печатной платы и компонентов. Экономия ресурсов налицо.

Когда плата уже собрана, но готовой прошивки еще нет, технология JTAG оказывается также чрезвычайно полезной на стадии программной отладки. В ПО JTAG ProVision™ заложена возможность создавать пользовательские функциональные приложения (JFT – JTAG Functional Test) на языке Python. Они удобны, не отягощены функционалом полноценных IDE и запускаются «на лету». При этом используются лишь JTAG-регистры компонента – никакая информация в ОЗУ или ПЗУ не записывается, ядро никак не участвует. Соответственно, за относительно небольшое время решается вопрос отладки будущей прошивки, пускай и на Python, а не в привычном С/С++, но главное здесь - подтвердить концепцию. С другой стороны, мы делаем функциональные приложения для включения их в итоговую тестовую последовательность. Автоматически генерируемые в ProVision™ приложения могут иметь ограниченную проверку периферийных компонентов. Например, у цифрового термометра может проверяться отклик по линии обращения I2C, но замер температуры не производиться. Для восполнения подобных задач и нужен JFT.

На одном из собственных изделий у нас таким способом была отлажена программа работы знакогенерирующего дисплея МЭЛТ (рис **⑤**), где в коде были допущены ошибки с последовательностью команд.

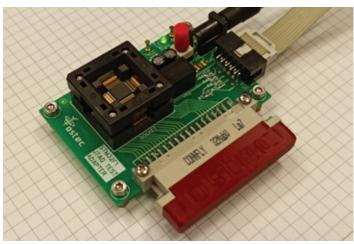

Для входного контроля микроконтроллеров STM32, используемых в собственных изделиях, предусмотрена спе-

циальная оснастка с сокетом под корпус LQFP-48 (рис **6**). Через JTAG-интерфейс проводится тест инфраструктуры, а также два теста соединений: сначала без замыкающего цепи разъема для поиска коротких замыканий, а затем с разъемом для поиска обрывов. Заказчикам предлагаются подобные решения входного контроля микросхем под необходимые корпуса, будь то BGA или QFP с большим числом выводов. Оснащение ПО ProVision™ опцией СогеСотрание позволяет заглянуть еще глубже и через JTAG-интерфейс проложить мост к внутренней архитектуре компонента. Через доступ к внутренней шине можно работать с памятью, протоколами обмена и управлять выводами там, например, где нет регистра периферийного сканирования.

## Заключение

В результате привлечения к тестированию технологий ICT и JTAG покрытие тестами некоторых наших изделий достигло 100 % и во многих случаях перекрывается. Как человек устойчиво стоит на двух ногах, так и электроконтроль печатных узлов в современной индустрии опирается с одной стороны на технологию периферийного сканирования для проверки цифровой части, а с другой стороны на внутрисхемное тестирование для выявления дефектов цепей и компонентов до подачи питания на изделие. Но мы не достигли потолка в DFT (Design for testability).

Собственные продукты активно развиваются, становятся сложнее и будут требовать вовлечения тех возможностей, которые не нужны сейчас. Например, может потребоваться не только тестирование за одно подключение к изделию, но и прошивка микросхем флэш-памяти и ПЛИС. Или использование цифро-аналоговых и частотных проверок с помощью модулей смешанных сигналов типа JT5112 от JTAG Technologies. Но уже сейчас можно сказать, что внедрение технологий тестирования дает нам неоспоримое преимущество как разработчику не только продвинутых, но и надежных решений.